# ST.ANNE'S

# **COLLEGE OF ENGINEERING AND TECHNOLOGY**

(An ISO 9001:2015 certified Institution) Anguchettypalayam, Panruti – 607 106

#### EE8681- MICROPROCESSOR AND MICROCONTROLLER LABORATORY

#### **OBSERVATION NOTE**

#### (FOR III B.E ELECTRICAL AND ELECTRONICS ENGINEERING STUDENTS)

| NAME           | :                         |

|----------------|---------------------------|

| REGISTER NO    | :                         |

| YEAR / SEMESTE | R: III Year / VI Semester |

AS PER ANNA UNIVERSITY (CHENNAI) SYLLABUS

2013 REGULATION

: DEC 2019 - MAR 2020

**PERIOD**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

PREPARED BY: Mr. S. BALABASKER, ASP/ECE

# ABOUT OBSERVATION NOTE & PREPARATION OF RECORD

- ❖ This Observation contains the basic diagrams of the circuits enlisted in the syllabus of EE8681- MICROPROCESSOR AND MICROCONTROLLER LABORATORY course, along with the design the design of various components of the circuit and controller.

- ❖ Aim of the experiment is also given at the beginning of each experiment. Once the student is able to design the circuit as per the circuit diagram, he/she is supposed to go through the instructions carefully and do the experiments step by step.

- \* They should note down the readings (observations) and tabulate them as specified.

- ❖ It is also expected that the students prepare the theory relevant to the experiment referring to prescribed reference book/journals in advance, and carry out the experiment after understanding thoroughly the concept and procedure of the experiment.

- ❖ They should get their observations verified and signed by the staff within two days and prepare & submit the record of the experiment while they come for the laboratory in subsequent week.

- ❖ The record should contain experiment No., Date ,Aim, Apparatus required, Theory, Procedure and result on one side(i.e., Right hand side, where rulings are provided) and Circuit diagram, Design, Model Graphs, Tabulations and Calculations on the other side (i.e., Left hand side, where no rulings is provided)

- ❖ All the diagrams and table lines should be drawn in pencil

- ❖ The students are directed to discuss & clarify their doubts with the staff members as and when required. They are also directed to follow strictly the guidelines specified.

### EE8681- MICROPROCESSOR AND MICROCONTROLLER LABORATORY

#### **SYLLABUS**

# **LIST OF EXPERIMENTS**

- 1. Simple arithmetic operations:

- (i) addition (ii) subtraction (iii) multiplication (iv) division.

- 2. Programming with control instructions:

- (i) Ascending / Descending order, Maximum / Minimum of numbers

- (ii) Programs using Rotate instructions

- (iii)Hex / ASCII / BCD code conversions.

- 3. Interface Experiments: with 8085

- (i) A/D Interfacing. & D/A Interfacing.

- 4. Traffic light controller.

- 5. I/O Port (8255)/ Serial communication(8251)

- 6. Programming Practices with Simulators/Emulators/open source

- 7. Read a key, interface display

- 8. Demonstration of basic instructions with 8051 Micro controller execution, including:

- (i) Conditional jumps, looping (ii) Calling subroutines.

- 9. Programming I/O Port 8051

- (i) Study on interface with A/D & D/A

- (ii) Study on interface with DC & AC motor .

- 10. Mini project development with processors.

# **OUTCOMES:**

At the end of the course, the student should be able to:

- ✓ Ability to understand and analyse, linear and digital electronic circuits.

- ✓ To understand and apply computing platform and software for engineering problems.

# **CYCLE I**

#### 8-bit Microprocessor

- 1. Simple arithmetic operations:

- (a) Addition (b) subtraction (c) multiplication (d) division.

- 2. Programming with control instructions:

- (a) Ascending order (b) Descending order

- (c) Maximum of numbers (d) Minimum of numbers.

- 3. Rotate instructions:

- 4. Code conversion.

- (a) ASCII to hexadecimal number (b) hexadecimal to ASCII(c) hexadecimal to decimal number (d) decimal to hexadecimal number

# 8085 Interfacing Program

- 5. Interface Experiments: (a) A/D Interfacing. (b) D/A Interfacing

- 6. Traffic light controller interfacing

- 7. I/O port Communication using 8255 & Serial Communication using 8251

- 8. Read a key using 8279 interface

- 9. Interface display using 8279 interface

- 10. 8085 Programming Practices with Simulators/ Jubin Open source Software

# **CYCLE II**

#### 8-bit Microcontroller

- 9. Demonstration of basic instructions with 8051 Micro controller execution, including:

- (a)Addition (b) subtraction (c) multiplication (d) division.

- (e) Conditional jumps, looping : Sum of elements in an array

- (f) Calling subroutines : Check whether given number is Odd or Even using call option

- 11. Programming I/O Port: (a) A/D Interfacing. (b) D/A Interfacing

- 12. Interface with DC & AC motor

- 13. Mini project development with processors

# **LIST OF EXPERIMENTS**

| S.NO | DATE | NAME OF THE EXPERIMENT | PAGE<br>NO | DATE OF<br>SUBMISSION | MARK (10) | SIGNATURE |

|------|------|------------------------|------------|-----------------------|-----------|-----------|

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

# **LIST OF EXPERIMENTS**

| S.NO | DATE | NAME OF THE EXPERIMENT | PAGE<br>NO | DATE OF<br>SUBMISSION | MARK (10) | SIGNATURE |

|------|------|------------------------|------------|-----------------------|-----------|-----------|

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

|      |      |                        |            |                       |           |           |

# 8085 MICROPROCESSOR EXPERIMENTS

| EXP NO: | SIMPLE ARITHMETIC OPERATIONS |

|---------|------------------------------|

| DATE    |                              |

#### AIM:

To write an assembly language program to add, multiply, divide and subtract two 8 bit numbers at two consecutive locations using 8085 microprocessor kit.

# **REQUIREMENTS:**

| S. No. | Hardware & Software Requirements | Quantity |

|--------|----------------------------------|----------|

| 1      | 8085 Trainer Kit                 | 1No      |

| 2      | Power Chord                      | 1No      |

| 3      | Opcode Sheet                     | 1 No     |

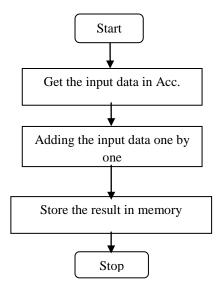

#### FLOWCHART FOR ADDITION

#### **ALGORITHM:**

- 1. Initialize memory pointer to data location.

- 2. Get the first number from memory in accumulator.

- 3. Get the second number and add it to the accumulator.

- 4. Store the answer at another memory location.

#### **ADDITION:**

| ADDRESS | LABEL | MNEMONICS  | OPCODE     | COMMENTS                              |  |

|---------|-------|------------|------------|---------------------------------------|--|

| 4100    |       | MVI A, 05H | 3E, 05     | Move immediate 05H data in Acc.       |  |

| 4102    |       | MVI B, 06H | 06, 06     | Move immediate 06H data in B register |  |

| 4104    |       | MVI C, 0AH | 0E, 0A     | Move immediate 0AH data in C register |  |

| 4106    |       | MVI D, 12H | 16, 12     | Move immediate 12H data in D register |  |

| 4108    |       | MVI E, 20H | IE, 20     | Move immediate 20H data in E register |  |

| 410A    |       | ADD B      | 80         | Adding Acc and B                      |  |

| 410B    |       | ADD C      | 81         | Adding Acc and C                      |  |

| 410C    |       | ADD D      | 82         | Adding Acc and D                      |  |

| 410D    |       | ADD E      | 83         | Adding Acc and E                      |  |

| 410F    |       | STA 4500   | 32, 00, 45 | Store the result                      |  |

| 4112    |       | HLT        | 76         | Stop the program                      |  |

#### **INPUT**

4100-04

4103-05

4105-0A

4107-12

4109-20

#### **OUTPUT**

4500-47

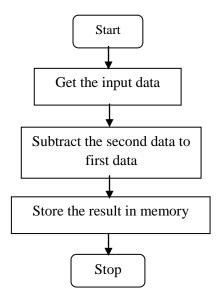

#### FLOWCHART FOR SUBTRACTION

#### **ALGORITHM**

- 1. The subtrahend stored in A register.

- 2. The minuend stored in B register.

- 3. Store the result in 4600.

#### **SUBTRACTION**

| ADDRESS | LABEL | MNEMONICS  | OPCODE     | COMMENTS                              |  |

|---------|-------|------------|------------|---------------------------------------|--|

| 4100    |       | MVI A, 05H | 3E, 05     | Move immediate the 05H data in Acc.   |  |

| 4102    |       | MVI B, 02H | 06, 02     | Move the data 02 data into B register |  |

| 4104    |       | SUB B      | 90         | Subtract data of Acc & B register.    |  |

| 4105    |       | STA 4600   | 32, 00, 46 | Store the result in 4600              |  |

| 4108    |       | HLT        | 76         | STOP the program.                     |  |

**INPUT:**

4100-05

4102-02

#### **OUTPUT:**

4A00-03

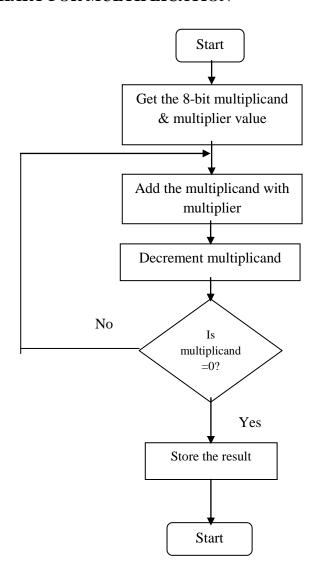

#### FLOWCHART FOR MULTIPLICATION

#### **MULTIPLICATION**

| ADDRESS | LABEL | MNEMONICS  | OPCODE     | COMMENTS                                |

|---------|-------|------------|------------|-----------------------------------------|

| 4100    |       | MVI B, 07H | 06, 07     | Move immediate data 05H into B register |

| 4102    |       | MVI C, 06H | 0E, 06     | Move immediate data 04H into B register |

| 4104    |       | XRA A      | AF         | XOR operation of Acc.                   |

| 4105    | GO:   | ADD B      | 80         | Adding Acc. & B register                |

| 4106    |       | DCR C      | OD         | Decrement C register                    |

| 4107    |       | JNZ GO     | C2, 05, 41 | Jump NO zero ON C register              |

| 410A    |       | STA 4A00   | 32, 00, 4A | Store the result                        |

| 410D    |       | HLT        | 76         | STOP the program                        |

#### **INPUT**

4100-07

4102-06

#### **OUTPUT**

4A00-2A

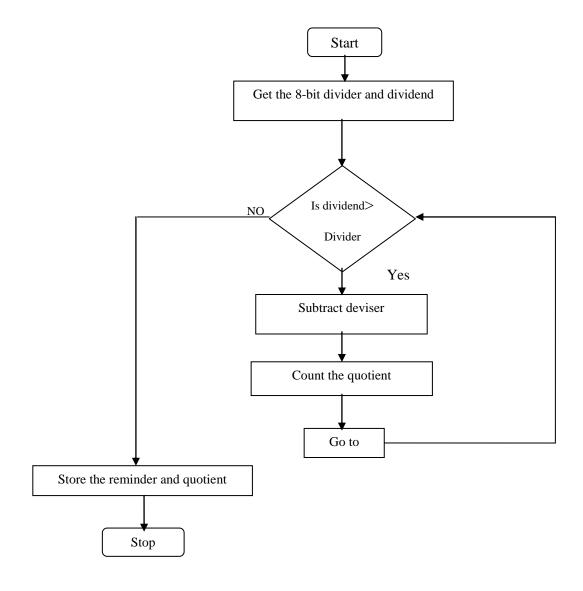

#### FLOWCHART FOR DIVISION

#### **DIVISION**

| ADDRESS | LABEL  | MNEMONICS  | OPCODE     | COMMENTS                                |  |

|---------|--------|------------|------------|-----------------------------------------|--|

| 4100    |        | MVI A, 25H | 3E, 25     | Move immediate data 0AH in Acc          |  |

| 4102    |        | MVI B, 05H | 06, 05     | Move immediate data into 'B' register   |  |

| 4104    |        | MVI C, 00H | 0E, 00     | Move immediate data 00H in 'C' register |  |

| 4106    | LOOP2: | CMP, B     | B8         | Compare Acc & 'B' register              |  |

| 4107    |        | JC LOOP1   | DA, OF, 41 | Jump with carry                         |  |

| 410A    |        | SUB, B     | 90         | Subtract Acc & 'B' register data        |  |

| 410B    |        | INR, C     | 0C         | Increment 'C' register                  |  |

| 410C    |        | JMP LOOP2  | C3, 06, 41 | Jump in 4106                            |  |

| 410F    | LOOP1: | STA 4B00   | 32,00, 4B  | Store the result 4A00                   |  |

| 4112    |        | MOV A, C   | 79         | Move 'C' into Acc                       |  |

| 4113    |        | STA 4B01   | 32, 01, 4B | Store the result                        |  |

| 4116    |        | HLT        | 76         | STOP the program                        |  |

#### **INPUT**

4100-25

4102-05

#### **OUTPUT**

4B00-02 (Reminder)

4B01-07(Quotient)

| C+ | Anno's | $\triangle$ ET |

|----|--------|----------------|

|    |        |                |

#### **RESULT**

Thus the above assembly language program for 8 bit Addition, subtraction, division and multiplication has been executed and the output results are verified.

| EXP NO: | PROGRAMMING WITH CONTROL INSTRUCTIONS |  |

|---------|---------------------------------------|--|

| DATE    | TROGRAMMING WITH CONTROL INSTRUCTIONS |  |

#### A) SMALLEST AND BIGGEST NUMBER

#### <u>AIM</u>

To write an assemble language program to find smallest and biggest number from the given set of values using 8085 Microprocessor kit.

#### **REQUIREMENTS:**

| S. No. | Hardware & Software Requirements | Quantity |

|--------|----------------------------------|----------|

| 1      | 8085 Trainer Kit                 | 1No      |

| 2      | Power Chord                      | 1No      |

| 3      | Opcode Sheet                     | 1 No     |

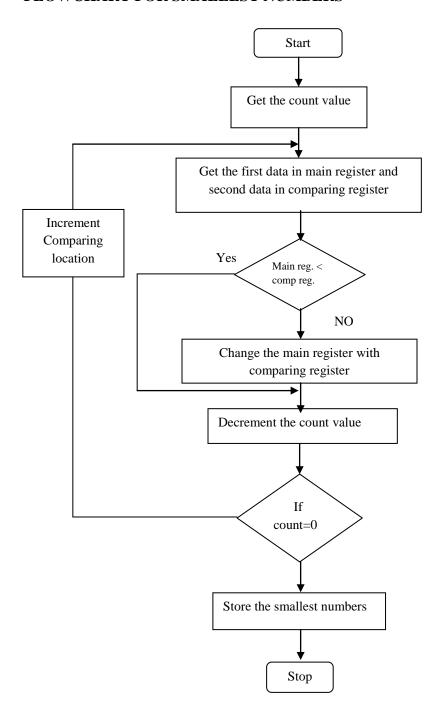

#### FLOWCHART FOR SMALLEST NUMBERS

#### **SMALLEST VALUE**

| ADDRESS | LABEL  | MNEMONICS   | OPCODE     | COMMENTS                                |  |

|---------|--------|-------------|------------|-----------------------------------------|--|

| 4100    |        | LXI H, 4200 | 21, 00, 42 | Load the data from given                |  |

| 4103    |        | MOV C, M    | 4E         | Move content M to 'C' register          |  |

| 4104    |        | MVI A, FF   | 3E, FF     | Move immediate data in Acc              |  |

| 4106    | Loop2: | IN X H      | 23         | Increment register pair (HL)            |  |

| 4107    |        | CMP M       | BE         | Compare memory to register              |  |

| 4108    |        | JC LOOP1    | DA,OC, 41  | Jump to carry LOOP1 If carry fly is set |  |

| 410B    |        | MOV A, M    | 7E         | Move count memory to Accumulator        |  |

| 410C    | Loop1: | DCR C       | OD         | Decrement 'C' register by one           |  |

| 410D    |        | JNZ LOOP2   | C2, 06, 41 | Jump to LOOP2                           |  |

| 4110    |        | STA 4207    | 32, 07, 42 | Store the result                        |  |

| 4113    |        | HLT         | 76         | STOP the program                        |  |

#### **OBSERVATION**

COUNT VALUE - 4200 - 04

#### **INPUT**

- 1) 4201 03

- 2) 4202 02

- 3) 4203 01

- 4) 4204 2F

#### **OUTPUT**

4207 - 01 Smallest value

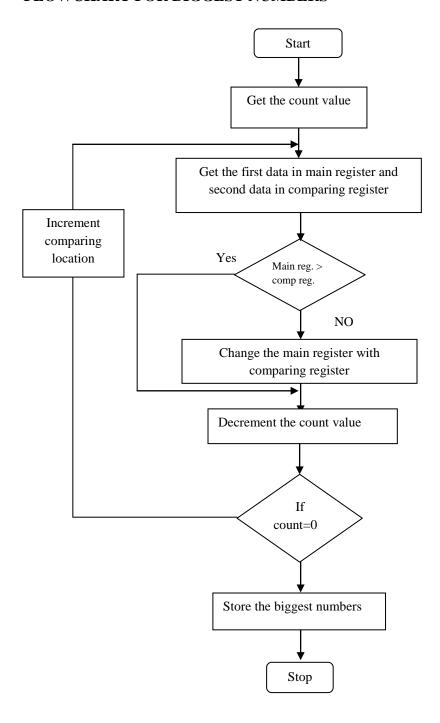

#### FLOWCHART FOR BIGGEST NUMBERS

#### **BIGGEST NUMBERS**

| ADDRESS | LABEL  | MNEMONICS   | OPCODE   | COMMENTS                            |  |

|---------|--------|-------------|----------|-------------------------------------|--|

| 4100    |        | LXI H, 4400 | 21,00,44 | Load the data from given            |  |

| 4103    |        | MOV C, M    | 4E       | Move content M to Acc               |  |

| 4104    |        | MVI A, 00   | 3E,00    | Clear the Accumulator               |  |

| 4106    | LOOP2: | IN X H      | 23       | Increment 'H' data address location |  |

| 4107    |        | CMP M       | BE       | Compare the Acc with M              |  |

| 4108    |        | JNC LOOP1   | D2,OC,41 | Jump ON no carry to LOOP1           |  |

| 410B    |        | MOVA, M     | 7E       | Move memory to Acc                  |  |

| 410C    | LOOP:  | DCR C       | OD       | Decrement the count                 |  |

| 410D    |        | JNZ LOOP2   | C2,06,41 | Jump NO zero on 'C' register        |  |

| 4112    |        | STA 4406    | 32,06,44 | Store the result                    |  |

| 4113    |        | HLT         | 76       | STOP the program                    |  |

#### **OBSERVATION:**

**COUNT VALUE - 4400 - 05**

#### **INPUT**

- 1) 4401 10

- 2) 4402 08

- 3)4403 04

- 4)4404 05

- 5)4405 02

#### **OUTPUT**

4406 - 10 Biggest value

| C+   | Λ   |      | CET |

|------|-----|------|-----|

| . IC | AII | me s | GEI |

#### **RESULT**

Thus the program for finding smallest and biggest number form given set of value has been executed and the output results are verified.

# **B) ASCENDING AND DESCENDING ORDER**

#### **AIM**

To write an assemble language program of ascending and descending order of N number.

# **REQUIREMENTS:**

| S. No. | Hardware & Software Requirements | Quantity |

|--------|----------------------------------|----------|

| 1      | 8085 Trainer Kit                 | 1No      |

| 2      | Power Chord                      | 1No      |

| 3      | Opcode Sheet                     | 1 No     |

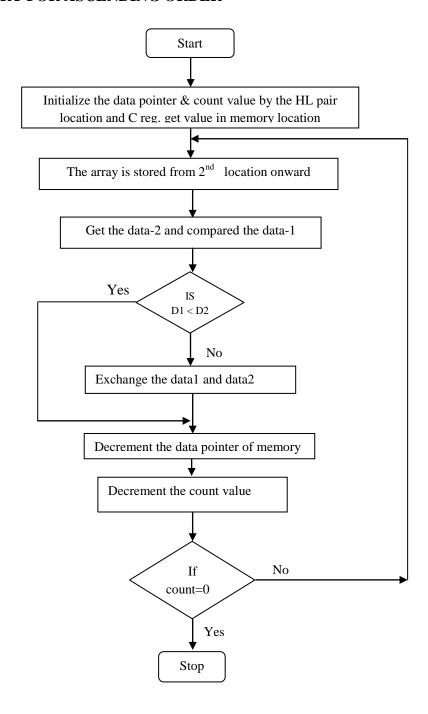

#### FLOWCHART FOR ASCENDING ORDER

#### **ASCENDING ORDER**

| ADDRESS | LABEL | MNEMONICS  | OPCODE     | COMMENTS                                                                                              |

|---------|-------|------------|------------|-------------------------------------------------------------------------------------------------------|

| 4100    | UPON: | MVIB, 00   | 06, 00     | Initialize the data pointer and count value                                                           |

| 4102    |       | LXIH, 4200 | 21,00,42   | Store the HL pair and Move the count value                                                            |

| 4105    |       | MOV C, M   | 4E         | Move the 'C' register to momery                                                                       |

| 4106    |       | INX H      | 23         | Increment the momery                                                                                  |

| 4107    |       | DCR C      | OD         | Decrement C                                                                                           |

| 4108    | REPT: | MOV A,M    | 7E         | Move first data to Accummulater                                                                       |

| 4109    |       | INX H      | 23         | increment HL pair                                                                                     |

| 410A    |       | CMP M      | BE         | Compare first data and 2 <sup>nd</sup> data                                                           |

| 410B    |       | JC DOWN    | DA, 14, 41 | If D1 <d2 2<sup="" and="" down="" exchange="" first="" jump="" otherwise="" the="" to="">nd data</d2> |

| 410E    |       | MOV D, M   | 56         |                                                                                                       |

| 410F    |       | MOV M, A   | 77         |                                                                                                       |

| 4110    |       | DCX H      | 2B         | Decrement count value                                                                                 |

| 4111    |       | MOV M,D    | 72         |                                                                                                       |

| 4112    |       | MVI B, 01  | 06,01      | Store '01' data to 'B' register                                                                       |

| 4114    | DOWN: | DCR C      | OD         | Decrement count value                                                                                 |

| 4115    |       | JNZ REPT   | C2,08,41   | Jump Non zero in counter to REPT                                                                      |

| 4118    |       | DCR B      | 05         |                                                                                                       |

| 4119    |       | JZ UPON    | CA,00,41   | If 'B' is zero Jump to UPON                                                                           |

| 411C    |       | HLT        | 76         | stop the program                                                                                      |

#### **OBSERVATION**

**COUNT VALUE - 4200 -09**

#### **INPUT**

1)4201- 06 (2)4202 - 01 (3)4203 - 0A (4)4204- 0F (5)4205 - 02 (6)4206 -03

(7)4207 -0B (8)4208-20 (9)4209-04

#### **OUTPUT**

$1)4201-\ 01\ (2)4202-02\ (3)4203-03\ (4)4204-04\ (5)4205-06\ (6)4206-0A$

(7)4207 -0B (8)4208-0F(9)4209-20

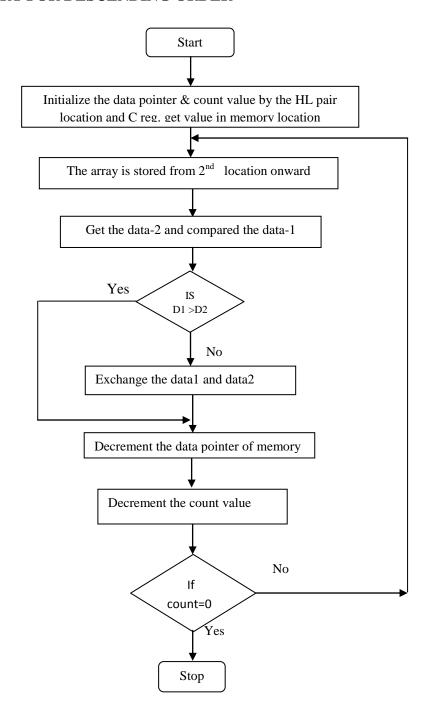

#### FLOWCHART FOR DESCENDING ORDER

#### **DESCENDING ORDER**

| ADDRESS | LABEL | MNEMONICS  | OPCODE     | COMMENTS                                                                                              |

|---------|-------|------------|------------|-------------------------------------------------------------------------------------------------------|

| 4100    | UPON: | MVIB, 00   | 06, 00     | Initialize the data pointer and count value                                                           |

| 4102    |       | LXIH, 4200 | 21,00,42   | Store the HL pair and Move the count value                                                            |

| 4105    |       | MOV C, M   | 4E         | Move the 'C' register to momery                                                                       |

| 4106    |       | INX H      | 23         | Increment the momery                                                                                  |

| 4107    |       | DCR C      | OD         | Decrement C                                                                                           |

| 4108    | REPT: | MOV A,M    | 7E         | Move first data to Accummulater                                                                       |

| 4109    |       | INX H      | 23         | increment HL pair                                                                                     |

| 410A    |       | CMP M      | BE         | Compare first data and 2 <sup>nd</sup> data                                                           |

| 410B    |       | JNC DOWN   | D2, 14, 41 | If D1 <d2 2<sup="" and="" down="" exchange="" first="" jump="" otherwise="" the="" to="">nd data</d2> |

| 410E    |       | MOV D, M   | 56         |                                                                                                       |

| 410F    |       | MOV M, A   | 77         |                                                                                                       |

| 4110    |       | DCX H      | 2B         | Decrement count value                                                                                 |

| 4111    |       | MOV M,D    | 72         |                                                                                                       |

| 4112    |       | MVI B, 01  | 06,01      | Store '01' data to 'B' register                                                                       |

| 4114    | DOWN: | DCR C      | OD         | Decrement count value                                                                                 |

| 4115    |       | JNZ REPT   | C2,08,41   | Jump Non zero in counter to REPT                                                                      |

| 4118    |       | DCR B      | 05         |                                                                                                       |

| 4119    |       | JZ UPON    | CA,00,41   | If 'B' is zero Jump to UPON                                                                           |

| 411C    |       | HLT        | 76         | stop the program                                                                                      |

#### **OBSERVATION**

COUNT VALUE -4200 -09

#### **INPUT**

1)4201- 06 (2)4202 - 01 (3)4203 - 0A (4)4204- 0F (5)4205 - 02 (6)4206 -03 (7)4207 -0B (8)4208-20 (9)4209-04

#### **OUTPUT**

1)4201- 20 (2)4202 - 0F (3)4203 - 0B (4)4204- 0A (5)4205 - 06 (6)4206 -04 (7)4207 -03 (8)4208-02 (9)4209-01

| C+  | ۸n  | ne's  | $\sim$ ET |

|-----|-----|-------|-----------|

| oı. | AII | 116.2 | GEI       |

#### **RESULT**

Thus the above assemble language program of ascending and descending order has been executed and the output results are verified.

| EXP NO: | PROGRAMMING WITH ROTATE INSTRUCTIONS |

|---------|--------------------------------------|

| DATE    | TROGRAMMING WITH ROTATE INSTRUCTIONS |

#### **AIM**

To write an assemble language program using rotate instruction in 8085 Microprocessor kit.

#### **REQUIREMENTS:**

| S. No. | Hardware & Software Requirements | Quantity |

|--------|----------------------------------|----------|

| 1      | 8085 Trainer Kit                 | 1No      |

| 2      | Power Chord                      | 1No      |

| 3      | Opcode Sheet                     | 1 No     |

#### THEORY:

#### **Rotate accumulator left (RLC):**

In this instruction, each bit is shifted to the adjacent left position. Bit D7 becomes D0. Carry flag CY is modified according to the bit D7.

A = D7 D6 D5 D4 D3 D2 D2 D0

A = 10101010; CY=0 //before the instruction

A = 01010101; CY=1 //after 1st RLC

A = 10101010; CY=0 //after 2nd RLC

#### Rotate accumulator left through carry (RAL):

In this instruction, each bit is shifted to the adjacent left position. Bit D7 becomes the carry bit and the carry bit is shifted into D0. Carry flag CY is modified according to the bit D7.

A = D7 D6 D5 D4 D3 D2 D2 D0

A = 10101010; CY=0 //before the instruction

A = 01010100; CY=1 //after 1st RAL

A = 10101001; CY=0 //after 2nd RAL

#### **Rotate accumulator right (RRC):**

In this instruction, each bit is shifted to the adjacent right position. Bit D7 becomes D0. Carry flag CY is modified according to the bit D0.

A = D7 D6 D5 D4 D3 D2 D2 D0

A = 10000001; CY=0 //before the instruction

A = 11000000; CY=1 //after 1st RRC

A = 01100000; CY=0 //after 2nd RRC

#### **Rotate accumulator right through carry (RAR):**

In this instruction, each bit is shifted to the adjacent right position. Bit D0 becomes the carry bit and the carry bit is shifted into D7. Carry flag CY is modified according to the bit D0.

A= D7 D6 D5 D4 D3 D2 D2 D0

A = 10000001; CY=0 //before the instruction

A = 01000000; CY=1 //after 1st RAR

A = 10100000; CY=0 //after 2nd RAR

#### **ROTATE INSTRUCTION**

| ADDRESS | LABEL | MNEMONICS  | OPCODE     | COMMENTS                               |

|---------|-------|------------|------------|----------------------------------------|

| 4100    |       | MVI A, 94H | 3E, 94     |                                        |

| 4102    |       | RLC        | 07         | Rotate accumulator left                |

| 4103    |       | STA 5000   | 32, 00, 50 |                                        |

| 4106    |       | RRC        | 0F         | Rotate accumulator right               |

| 4107    |       | STA 5001   | 32, 01, 50 |                                        |

| 410A    |       | RAR        | 1F         | Rotate accumulator right through carry |

| 410B    |       | STA 5002   | 32, 02, 50 |                                        |

| 410E    |       | RAL        | 17         | Rotate accumulator left through carry  |

| 410F    |       | STA 5003   | 32,02,50   |                                        |

| 4112    |       | HLT        | 76         |                                        |

#### **INPUT**

4100-94

#### **OUTPUT**

1)5000-29

2)5001-94

3)5002-CA

4)5003-94

| $^{\circ}$ | Anno's | $\triangle$ ET |

|------------|--------|----------------|

|            |        |                |

#### **RESULT**

Thus the above assemble language program rotate instruction has been executed and the output results are verified.

| EXP NO: | CODE CONVERSION |

|---------|-----------------|

| DATE    | CODE CONVERSION |

#### AIM:

To write an assembly language program to perform the conversions of BCD to hexadecimal number, hexadecimal to BCD, hexadecimal to ASCII, ASCII to hexadecimal number.

# **REQUIREMENTS:**

| S. No. | Hardware & Software Requirements | Quantity |

|--------|----------------------------------|----------|

| 1      | 8085 Trainer Kit                 | 1No      |

| 2      | Power Chord                      | 1No      |

| 3      | Opcode Sheet                     | 1 No     |

# **A) BCD TO HEX CONVERSION**

#### **ALGORITHM:**

- 1) Initialize memory pointer to 4150 H

- 2) Get the Most Significant Digit (MSD)

- 3) Multiply the MSD by ten using repeated addition

- 4) Add the Least Significant Digit (LSD) to the result obtained in previous step

- 5) Store the HEX data in Memory

#### **PROGRAM:**

```

LXI H,4150

```

MOV A,M // Initialize memory pointer

ADD A // MSD X 2

MOV B,A // Store MSD X 2

ADD A // MSD X 4

ADD A // MSD X 8

ADD B // MSD X 10

INX H // Point to LSD

ADD M // Add to form HEX

INX H

MOV M,A // Store the result

HLT

#### **OBSERVATION:**

#### **INPUT:**

4150:02 (MSD)

4151:09 (LSD)

#### **OUTPUT:**

4152:1D

# **B) HEX TO BCD CONVERSION**

#### **ALGORITHM:**

- 1) Initialize memory pointer to 4150 H

- 2) Get the Hexa decimal number in C register

- 3) Perform repeated addition for C number of times

- 4) Adjust for BCD in each step

- 5) Store the BCD data in Memory

#### **PROGRAM:**

```

LXI H,4150 // Initialize memory pointer

MVI D,00 // Clear D- reg for Most significant Byte

XRA A // Clear Accumulator

MOV C,M // Get HEX data

```

LOOP2: ADI 01 // Count the number one by one

DAA// Adjust for BCD count

JNC LOOP1

INR D

#### LOOP1: DCR C

JNZ LOOP2

STA 4151 // Store the Least Significant Byte

MOV A,D

STA 4152 // Store the Most Significant Byte

HLT

#### **OBSERVATION:**

#### **INPUT**:

4150: FF

#### **OUTPUT**:

4151 : 55 (LSB) 4152 : 02 (MSB)

# C) HEX TO ASCII CONVERSION

#### **ALGORITHM:**

- 1. Load the given data in A- register and move to B register

- 2. Mask the upper nibble of the Hexa decimal number in A register

- 3. Call subroutine to get ASCII of lower nibble

- 4. Store it in memory

- 5. Move B –register to A register and mask the lower nibble

- 6. Rotate the upper nibble to lower nibble position

- 7. Call subroutine to get ASCII of upper nibble

- 8. Store it in memory

- 9. Terminate the program.

#### **PROGRAM:**

```

LDA 4200 // Get Hexa Data

MOV B,A

ANI 0F

// Mask Upper Nibble

CALL SUB1

// Get ASCII code for upper nibble

STA 4201

MOV A,B

ANI F0

// Mask Lower Nibble

RLC

RLC

RLC

RLC

// Get ASCII code for lower nibble

CALL SUB1

STA 4202

HLT

SUB1: CPI 0A

JC SKIP

ADI 07

SKIP:

ADI 30

RET

```

#### **OBSERVATION:**

**INPUT**:

4200 - E4(Hexa data)

#### **OUTPUT**:

4201 - 34(ASCII Code for 4)

4202 - 45(ASCII Code for E)

# D) ASCII TO HEX CONVERSION

#### **ALGORITHM:**

- 1. Load the given data in A- register

- 2. Subtract 30 H from A register

- 3. Compare the content of A register with 0A H

- 4. If A < 0A H, jump to step6. Else proceed to next step.

- 5. Subtract 07 H from A register

- 6. Store the result

- 7. Terminate the program

#### **PROGRAM**

LDA 4500

**SUI 30**

CPI 0A

**JC SKIP**

**SUI 07**

SKIP: STA 4501

HLT

## **OBSERVATION:**

**INPUT**:

4500 - 31

**OUTPUT**:

4501 - 01

## **RESULT:**

Thus the assembly language program to perform the conversions of BCD to hexadecimal number, hexadecimal to BCD, hexadecimal to ASCII, ASCII to hexadecimal number has been executed and the output results are verified.

| EXP NO: | INTERFACING OF ADC AND DAC  |

|---------|-----------------------------|

| DATE    | INTERPACTION OF ADE AND DAC |

## A) ANALOG TO DIGITAL CONVERTOR

#### **AIM**

To write an assembly language program to convert an analog signal into a digital and to store the digital data in memory

## **REQUIREMENTS:**

| S. No. | Hardware & Software Requirements | Quantity |

|--------|----------------------------------|----------|

| 1      | 8085 Trainer Kit                 | 1No      |

| 2      | Power Chord                      | 1No      |

| 3      | Opcode Sheet                     | 1 No     |

| 4      | ADC interface Board              | 1 No     |

#### **PROBLEM STATEMENT:**

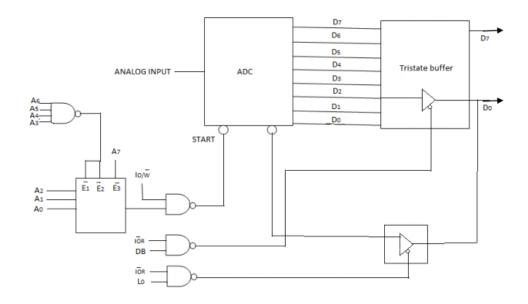

To program starts from memory location 4100H. The program is executed for various values of analog voltage which are set with the help of a potentiometer. The LED display is verified with the digital value that is stored in the memory location 4150H.

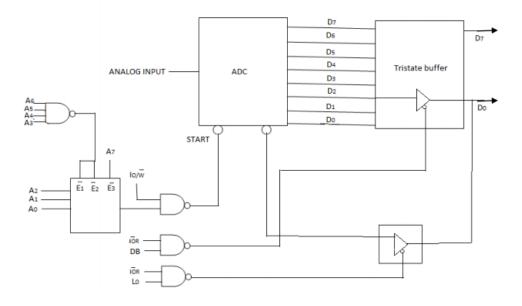

#### THEORY:

An ADC usually has two additional control lines: the SOC input to tell the ADC when to start the conversion and the EOC output to announce when the conversion is complete. The following program initiates the conversion process, checks the EOC pin of ADC 0419 as to whether the conversion is over and then inputs the data to the

## **CIRCUIT DIAGRAM:**

#### NOTE

- 1) Converter the analog signal in to digital and store the result in some memory location.

- 2) 4100 starting of use address.

- 3) 4500 result stored location.

## **SOC JUMPER SELECTION:**

J2: SOC Jumper selection

J5: Channel selection

#### **OBSERVATION:**

Compare the data displayed at the LEDs with that stored at location 4150

## **PROGRAM:**

MVI A,10

OUT C8

MVI A,18

OUT C8

MVI A,01

OUT D0

MVI A,00

OUT D0

LOOP: IN D8

**ANI 01**

**CPI 01**

JNZ LOOP

IN C0

STA 4150

HLT

## **OUTPUT:**

| ANALOG<br>VOLTAGE | DIGITAL DATA ON LED DISPLAY |    |    |    |    |    |    | HEX CODE<br>IN LOCATION 4150 |        |  |

|-------------------|-----------------------------|----|----|----|----|----|----|------------------------------|--------|--|

|                   | D7                          | D6 | D5 | D4 | D3 | D2 | D1 | D0                           | OUTPUT |  |

|                   |                             |    |    |    |    |    |    |                              |        |  |

|                   |                             |    |    |    |    |    |    |                              |        |  |

|                   |                             |    |    |    |    |    |    |                              |        |  |

|                   |                             |    |    |    |    |    |    |                              |        |  |

|                   |                             |    |    |    |    |    |    |                              |        |  |

|                   |                             |    |    |    |    |    |    |                              |        |  |

## **RESULT:**

Thus the assembly language program to convert an analog signal into a digital has been executed successfully and the digital data was stored at desired location.

## **B) DIGITAL TO ANALOG CONVERTOR**

#### AIM:

To interface DAC with 8085 to demonstrate the generation of square, saw tooth and triangular wave.

## **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | 8085 Trainer Kit                 | 1No      |

| 2    | Power Chord                      | 1No      |

| 3    | Opcode Sheet                     | 1 No     |

| 4    | DAC interface Board              | 1 No     |

#### THEORY:

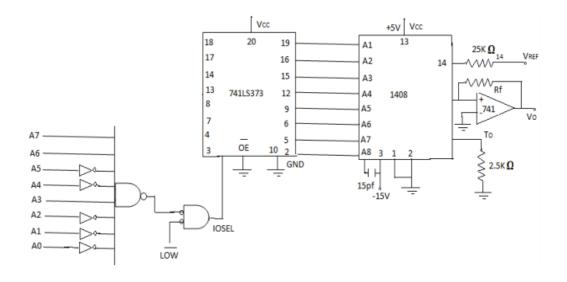

DAC 0800 is an 8 – bit DAC and the output voltage variation is between – 5V and + 5V. The output voltage varies in steps of 10/256 = 0.04 (appx.). The digital data input and the corresponding output voltages are presented in the below Table.

| Input Data in HEX | Output Voltage |

|-------------------|----------------|

| 00                | - 5.00         |

| 01                | - 4.96         |

| 02                | - 4.92         |

| 7F                | 0.00           |

| FD                | 4.92           |

| FE                | 4.96           |

| FF                | 5.00           |

Referring to above table, with 00 as input to DAC, the analog output is -5V. Similarly, with FF as input, the output is +5V. Outputting digital data 00 and FF at regular intervals, to DAC, results in different wave forms namely square, triangular, etc., The port address of DAC is 08 H.

## **CIRCUIT DIAGRAM:**

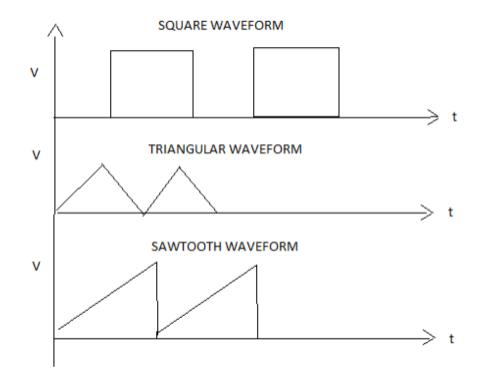

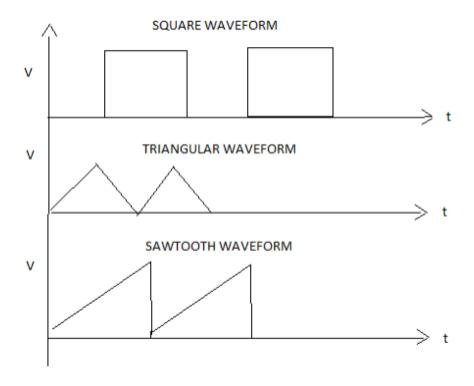

#### **WAVEFORMS:**

## **SQUARE WAVE GENERATION**

#### **ALGORITHM:**

- 1. Load the initial value (00) to Accumulator and move it to DAC

- 2. Call the delay program

- 3. Load the final value(FF) to accumulator and move it to DAC

- 4. Call the delay program.

- 5. Repeat Steps 2 to 5

#### **PROGRAM**

START: MVI A,00

OUT C8

**CALL DELAY**

MVI A,FF

OUT C8

CALL DELAY

JMP START

DELAY: MVI B,05

L1: MVI C,FF

L2: DCR C

JNZ L2

DCR B

JNZ L1

**RET**

| AMPLITUDE | TIME PERIOD |

|-----------|-------------|

|           |             |

#### TRIANGULAR WAVE GENERATION

#### **ALGORITHM:**

- 1. Load the initial value (00) to Accumulator

- 3. Move the accumulator content to DAC

- 4. Increment the accumulator content by 1.

- 5. If accumulator content is zero proceed to next step. Else go to step 3.

- 6. Load value (FF) to Accumulator

- 7. Move the accumulator content to DAC

- 8. Decrement the accumulator content by 1.

- 9. If accumulator content is zero go to step2. Else go to step 7.

#### **PROGRAM**

START: MVI L,00

L1: MOV A,L

OUT C8

INR L

JNZ L1

MVI L,FF

L2: MOV A,L

OUT C8

DCR L

JNZ L2

JMP START

| AMPLITUDE | TIME PERIOD |

|-----------|-------------|

|           |             |

#### **SAW TOOTH WAVE GENERATION**

#### **ALGORITHM:**

- 1. Load the initial value (00) to Accumulator

- 2. Move the accumulator content to DAC

- 3. Increment the accumulator content by 1.

- 4. Repeat Steps 3 and 4.

## **PROGRAM:**

START: MVI A,00

L1: OUT C8

INR A

JNZ L1

JMP START

| AMPLITUDE | TIME PERIOD |

|-----------|-------------|

|           |             |

| St. Anne's CET | EE6612- MICROPROCESSORS AND MICRO CONTROLLERS LABORATORY |

|----------------|----------------------------------------------------------|

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

## **RESULT**

Thus the above interface assembler language digital to analog converter is verified.

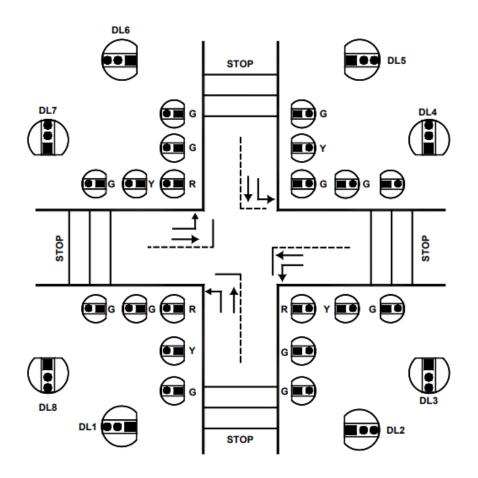

| EXP NO: | TRAFFIC LIGHT CONTROLLER |

|---------|--------------------------|

| DATE    | TRAFFIC LIGHT CONTROLLER |

#### AIM:

To write an assembly language program to simulate the traffic light at an intersection using a traffic light interface.

### **REQUIREMENTS:**

| S. No. | Hardware & Software Requirements         | Quantity |

|--------|------------------------------------------|----------|

| 1      | 8085 Trainer Kit                         | 1No      |

| 2      | Power Chord                              | 1No      |

| 3      | Opcode Sheet                             | 1 No     |

| 4      | Traffic Light Controller Interface Board | 1No      |

## A SAMPLE SEQUENCE:

- 1. (a) Vehicles from south can go to straight or left.

- (b) Vehicles from west can cross the road.

- (c) Each pedestrian can cross the road.

- (d) Vehicles from east no movement.

- (e) Vehicles from north can go only straight.

- 2. All ambers are ON, indicating the change of sequence.

- 3. (a) Vehicles from east can go straight and left.

- (b) Vehicles from south can go only left.

- (c) North pedestrian can cross the road.

- (d) Vehicles from north, no movement.

- (e) Vehicles from west can go only straight.

- 4. All ambers are ON, indicating the change of sequence.

- 5. (a) Vehicles from north can go straight and left.

- (b) Vehicles from east can go only left.

- (c) West pedestrian can cross the road.

- (d) Vehicles from west, no movement.

- (e) Vehicles from south can go only straight.

- 6. All ambers are ON, indicating the change of sequence.

- 7. (a) Vehicles from west can go straight and left.

- (b) Vehicles from north can go only left.

- (c) South pedestrian can cross the road.

- (d) Vehicles from south, no movement.

- (e) Vehicles from east can go only straight.

- 8. All ambers are ON, indicating the change of sequence.

- 9. (a) All vehicles from all directions no movement.

- (b) All pedestrian can cross the road.

## **ALGORITHM:**

- 1. Initialize 8255, port A and port B in output mode

- 2. Send data on PA to glow R1 and R2.

- 3. Send data on PB to glow G3 and G4.

- 4. Load multiplier count (40) for delay.

- 5. Call delay subroutine.

- 6. Send data on PA to glow Y1 and Y2.

- 7. Send data on PB to glow Y3 and Y4.

- 8. Load multiplier count (10) for delay.

- 9. Call delay subroutine.

- 10. Send data on PA to glow G1 and G2.

- 11. Send data on PB to glow R3 and R4.

- 12.Load multiplier count (40) for delay.

- 13.Call delay subroutine.

- 14. Send data on PA to glow Y1 and Y2.

- 15. Send data on PA to glow Y3 and Y4.

- 16.Load multiplier count (10) for delay.

- 17. Call delay subroutine

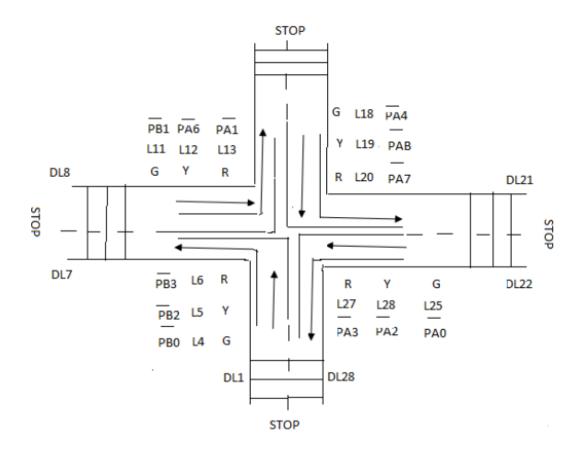

## **HARDWARE LAYOUT**

# **PIN LAYOUT**

| BIT | LED         | BIT | LED         | BIT | LED            |

|-----|-------------|-----|-------------|-----|----------------|

| PA0 | SOUTH LEFT  | PB0 | NORTH LEFT  | PC0 | WEST STRAIGHT  |

| PA1 | SOUTH RIGHT | PB1 | NORTH RIGHT | PC1 | NORTH STRAIGHT |

| PA2 | SOUTH AMBER | PB2 | NORTH AMBER | PC2 | EAST STRAIGHT  |

| PA3 | SOUTH RED   | PB3 | NORTH RED   | PC3 | SOUTH STRAIGHT |

| PA4 | EAST LEFT   | PB4 | WEST LEFT   | PC4 | NORTH PD       |

| PA5 | EAST RIGHT  | PB5 | WEST RIGHT  | PC5 | WEST PD        |

| PA6 | EAST AMBER  | PB6 | WEST AMBER  | PC6 | SOUTH PD       |

| PA7 | EAST RED    | PB7 | WEST RED    | PC7 | EAST PD        |

## **CONTROL:**

CONTROL ---- 0F (FOR 8255 PPI)

PORT A---- 0C

PORT B ---- 0D

PORT C ---- 0E

## **PROGRAM:**

START: LXI H,4500

MVI C,04

MOV A,M

OUT 0F

INX H

LOOP1: MOV A,M

OUT 0C

INX H

MOV A,M

OUT 0D

**CALL DELAY**

INX H

DCR C

JNZ LOOP1

JMP START

**DELAY: PUSH B**

MVI C,05

LOOP3: LXI D,FFFF

LOOP2: DCX D

MOV A,D

ORA E

JNZ LOOP2

DCR C

JNZ LOOP3

POP B

**RET**

#### **OBSERVATION**

- 4500-80

- 4501-1A

- 4502-A1

- 4503-64

- 4504-A4

- 4505-81

- 4506-5A

- 4507-64

- 4508-54

- 4509-8A

- 450A-B1

- 450B -A8

- 450C-B4

- 450D -88

- 450E -DA

- 450F -68

- 4510 -D8

- 4511 -1A

- 4512 -E8

- 4513 -46

- 4514 -E8

- 4515 -83

- 4516 78

- 4517-86

- 4518 -74

## **RESULT:**

Thus an assembly language program to simulate the traffic light at an intersection using a traffic light interfaces was written and implemented.

| EXP NO: | I/O PORT INTERFACING |

|---------|----------------------|

| DATE    | DOTORI INTERFACING   |

#### AIM:

$\label{eq:total perform read and write operation using 8085 kit} To interface 8255 PPI with microprocessor and to perform read and write operation using 8085 kit$

#### **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | 8085 Trainer Kit                 | 1No      |

| 2    | Power Chord                      | 1No      |

| 3    | Opcode Sheet                     | 1 No     |

| 4    | 8255 Interface board             | 1No      |

#### PERFORMING OPERATION

- i) Read the data from Accumulator (use LED)

- ii) Read the data to Accumulator (DIP switch)

#### **NOTE**

- i. Use port A as input

- ii. Use port B and C as output

- iii. Address of the post are given below

- a. Port A(PA) C0

- b. Port B(PB) C2

- c. Port C(PC) C4

- d. Control Register(CR) C6

- e. Control Word(CW) 90

#### **PROGRAM**

| ADDRESS | LABEL | MNEMONICS | OPCODE   | COMMENTS                                   |

|---------|-------|-----------|----------|--------------------------------------------|

| 4100    |       | MVIA, CW  | 3E, 90   | Initializations of control words           |

| 4102    |       | OUT CR    | D3,C6    | Initializations of output control register |

| 4104    |       | MVI A, 05 | 3E,05    | Move 05 data to accumulator                |

| 4106    |       | OUT PB    | D3, C2   | Initializations of port B as output        |

| 4108    |       | IN PA     | DB, C0   | Initializations of port A as input         |

| 410A    |       | STA 4500  | 32,00,45 | Store the accumulator result in 4500       |

| 410D    |       | HLT       | 76       | Stop the program                           |

## **RESULT**

Thus the 8255 peripheral IC is interfaced with microprocessor and performs the READ/WRITE operation is verified

| EXP NO: | SERIAL COMMUNICATION |

|---------|----------------------|

| DATE    | SERIAL COMMUNICATION |

#### AIM:

To write a program to initiate 8251 and to check the transmission and reception of character.

#### **REQUIREMENTS:**

| S.<br>No. | Hardware & Software Requirements | Quantity |

|-----------|----------------------------------|----------|

| 1         | 8085 Trainer Kit                 | 1No      |

| 2         | Power Chord                      | 1No      |

| 3         | Opcode Sheet                     | 1 No     |

| 4         | 8251 Interface board             | 1 No     |

| 5         | VXT parallel bus/ RS 232C cable  | Few      |

#### THEORY:

The 8251 is used as a peripheral device for serial communication and is programmed by the CPU to operate using virtually any serial data transmission technique. The USART accepts data characters from the CPU in parallel format and the converts them in a continuous serial data stream of transmission. Simultaneously, it can receive serial data streams and convert them into parallel data characters for the CPU. The CPU can read the status of USART at any time. These include data transmissions errors and control signals.

Prior to starting data transmission or reception, the 8251 must be loaded with a set of control words generated by the CPU. These control signals define the complete functional definition of the 8251 and must immediately follow a RESET operation. Control words should be written in to the control register of 8251. Words should be written in to the control register of 8251. words should be written in to the control register of 8251. These control words are split into two formats.

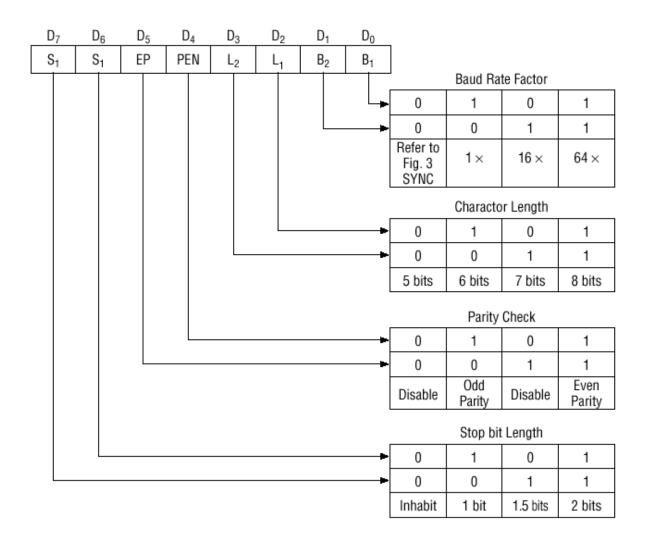

- 1. MODE INSTRUCTION WORD

- 2. COMMAND INSTRUCTION WORD.

#### 1. MODE INSTRUCTION WORD

This format defines the BAUD rate, character length, parity and stop bits required to work with asynchronous data communication. By selecting the appropriate BAUD factor synchronous mode, the 8251 can be operated in synchronous mode. Initializing 8251 using the Mode instructions to the following conditions

```

8 \text{ bit data}

No \text{ parity}

16x \text{ Baud rate factor}

1 \text{ stop bit}

B2, B1 = 1, 0

L2, L1 = 1, 1

PEN = 0

EP = 0

S2, S1 = 0, 1

gives a Mode command word of 4E.

```

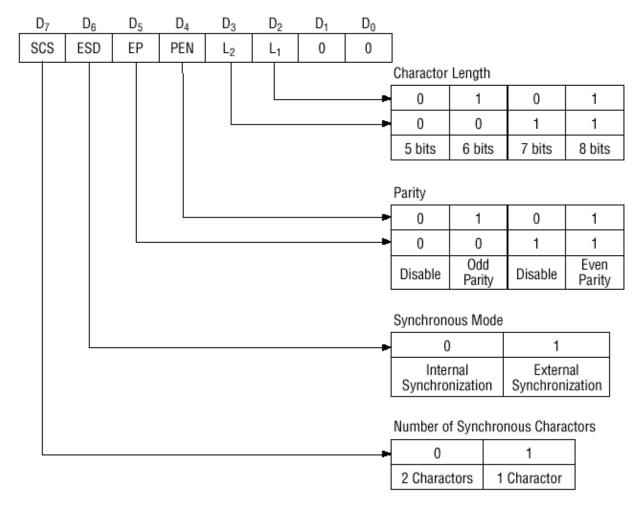

Fig. 2 Bit Configuration of Mode Instruction (Asynchronous)

Fig. 3 Bit Configuration of Mode Instruction (Synchronous)

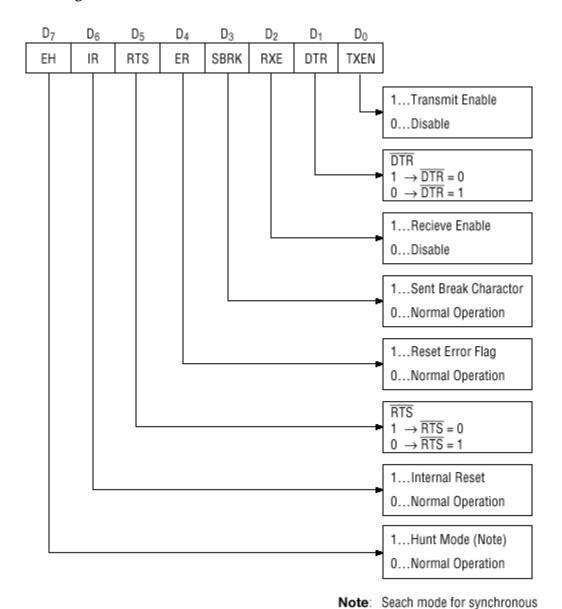

#### 2. COMMAND INSTRUCTION WORD

This format defines a status word that is used to control the actual operation of 8251. All control words written into 8251 after the mode instruction will load the command instruction. The command instructions can be written into 8251 at any time in the data block during the operation of the 8251, to return to the mode instruction format, the master reset bit in the command instruction word can be set to initiate an internal reset operation which automatically places the 8251 back into the mode instruction format. Command instructions must follow the mode instructions or sync characters. Thus the control word 37 (HEX) enables the transmit enable and receive enable bits, forces DTR output to zero, resets the error flags, and forces RTS output to zero.

When 8251A is initialized as follows using the command instruction,

Reset Error flags, Enable transmission and reception, Make RTS and DTR active low.

$\begin{aligned} EH &= 0 & SBRK &= 0 \\ IR &= 0 & RxE &= 1 \\ RTS &= 1 & DTR &= 1 \\ ER &= 1 & TxEN &= 1 \end{aligned}$

We get a command word of 37

Fig. 4 Bit Configuration of Command

The program after initializing, will read the status register and check for TxEMPTY. If the transmitter buffer is empty then it will send 31 to the serial port and then check for a character in the receive buffer. If some character is present then, it is received and stored at location 4200H.

charactors in synchronous mode.

## TRANSMITTER: Starting address: 4100

MVI A, 36

**OUT CE**

MVI A,0A

OUT C8

MVI A,00

OUT C8

MVI A,4E

OUT C2

MVI A,37

OUT C2

MVI A,31

OUT CO

RST 1

# **RECEIVER: Starting address: 4200**

IN C0

STA 4150

RST 1

#### **OBSERVATION:**

Feed the above program 4100 acts as Transmitter and 4200 acts as Receiver. Execute the two programs simultaneously. Check the Receiver at location 4150H. It's content will be 31.

| INPUT DATA | OUTPUT DTA |

|------------|------------|

|            |            |

#### **RESULT:**

Thus the assembly language program for transmission and reception of character was executed and verified successfully by interfacing 8251 with 8085.

| EXP NO: | INTERFACE DISPLAY |

|---------|-------------------|

| DATE    | INTERFACE DISTER  |

## AIM:

To interface 8279 Programmable Keyboard Display Controller to 8085 Microprocessor

# **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | 8085 Trainer Kit                 | 1No      |

| 2    | Power Chord                      | 1No      |

| 3    | Opcode Sheet                     | 1 No     |

| 4    | 8279 Interface board             | 1 No     |

| 5    | VXT parallel bus, RS 232C cable  | 1 No     |

#### **DISPLAY PROGRAM:**

START: LXI H,4130

MVI D,0F // Initialize counter

MVI A,10

OUT C2 // Set Mode and Display

MVI A,CC // Clear display

OUT C2

MVI A,90 // Write Display

OUT C2

LOOP: MOV A,M

OUT C0

CALL DELAY

INX H

DCR D

JNZ LOOP

JMP START

DELAY: MVI B,A0

LOOP2: MVI C,FF

LOOP1: DCR C

JNZ LOOP1

DCR B

JNZ LOOP2

**RET**

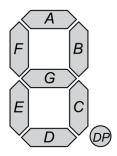

## **SEVEN SEMENT DETAILS:**

| DATA BUS | <b>D7</b> | D6 | D5 | D4 | D3 | D2 | D1 | <b>D</b> 0 |

|----------|-----------|----|----|----|----|----|----|------------|

| SEGMENTS | D         | C  | В  | A  | DP | G  | F  | E          |

| LETTER | SEGMENT |    |    |    |    |    |    |    |    |             |

|--------|---------|----|----|----|----|----|----|----|----|-------------|

|        |         | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | HEXADECIMAL |

|        |         |    |    |    |    |    |    |    |    |             |

|        |         |    |    |    |    |    |    |    |    |             |

#### **INPUT:**

- 4130 FF

- 4131 -FF

- 4132 -FF

- 4133 -FF

- 4134 -FF

- 4135 -FF

- 4136 -FF

- 4137 –FF

- 4138 -FF

- 4139 -FF

- 413A -FF

- 413B -FF

- 413C -FF

- 413D -FF

- 413E -FF

- 413F -FF

#### **RESULT:**

Thus 8279 Controller was interfaced with 8085 and Rolling Display was executed Successfully and the output is verified.

| EXP NO: | READ A KEY |

|---------|------------|

| DATE    | KEAD A KET |

## AIM:

To interface 8279 Programmable Keyboard Display Controller to 8085 Microprocessor

# **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | 8085 Trainer Kit                 | 1No      |

| 2    | Power Chord                      | 1No      |

| 3    | Opcode Sheet                     | 1 No     |

| 4    | 8279 Interface board             | 1No      |

| 5    | VXT parallel bus, RS 232C cable  | Few      |

#### **KEYBOARD PROGRAM:**

**MVI B,08**

**MVI A,02**

OUT C2

MVI A,CC

OUT C2

MVI A,90

OUT C2

MVI A,FF

BACK: OUT CO

DCR B

JNZ BACK

LOP: IN C2

**ANI 07**

JZ LOP

MVI A,40

OUT C2

IN C0

ANI 0F

MOV L,A

**MVI H,42**

MOV A,M

OUT CO

JMP LOP

- 4200 0C

- 4201 9F

- 4202- 4A

- 4203 0B

- 4204 99

- 4205 29

- 4206 28

- 4207 8F

- 4208 08

- 4209 09

- 420A 88

- 420B 38

- 420C 6C

- 420D 1A

| St. Anne's CET | EE6612- MICROPROCESSORS AND MICRO CONTROLLERS LABORATORY |

|----------------|----------------------------------------------------------|

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

|                |                                                          |

## **RESULT:**

Thus 8279 Controller was interfaced with 8085 and Program for Read Key was Executed Successfully.

| EXP NO: | PROGRAMMING PRACTICES WITH SIMULATORS  |

|---------|----------------------------------------|

| DATE    | TROGRAMMING TRACTICES WITH SINICEATORS |

To write an assembly language program to add the given data stored at two consecutive locations using 8085 microprocessor simulator.

#### **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | Jubin Open source Software       | 1No      |

| 2    | PC                               | 1No      |

#### **THEORY**

Understanding of Intel 8085 microprocessor is fundamental to getting insight into the Von-Neumann Architecture. It was first introduced in 1976, since then many generations of computer architecture have come up, some still persists while others are lost in history. This microprocessor still survives because it is still popular in university and training institutes to get students acquainted with basic computer architecture. For this purpose 8085 trainer kit are available on the market. With this academic learning purpose in mind 8085 simulator software is designed. It helps in get started easily with example codes, and to learn the architecture playfully. It also provides a trainer kit as an appealing functional alternative to real hardware. The users can write assembly code easily and get results quickly without even having the actual hardware. Jubin 8085 simualor is open source software which is available at

https://8085simulator.codeplex.com/downloads/get/86234

#### **PROGRAM**

**MVI A,05**

**MVI B,06**

MVI C,0A

MVI D,12

**MVI E,20**

ADD B

ADD C

ADD D

ADD E

STA 4500

HLT

#### **OBSERVATION:**

#### **INPUT**

4100-04

4103-05

4105-0A

4107-12

4109-20

#### **OUTPUT**

4500-47

#### **RESULT**

Thus the addition of two numbers was performed using the 8085 microprocessor simulator.

# 8051 MICROCONTROLLER EXPERIMENTS

| EXP NO: | SIMPLE ARITHMETIC OPERATION |

|---------|-----------------------------|

| DATE    | SIMILE ARTHMETIC OF EXATION |

To perform 8 bit addition, subtraction multiplication and division using immediate addressing in microcontroller (8051) and store result in memory.

# **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | 8051 Trainer Kit                 | 1No      |

| 2    | Power Chord                      | 1No      |

| 3    | Keyboard                         | 1 No     |

#### NOTE:

A <enter>→ Address GO <address><enter> SP<address> <enter> U<enter><address>

#### A) ADDITION

| ADDRESS | LABEL | MNEMONICS        | OPCODE   | COMMENTS                   |

|---------|-------|------------------|----------|----------------------------|

| 4100    |       | CLR C            | C3       | Clear the carry            |

| 4101    |       | MOV A, # 20      | 74,20    | Get the first data         |

| 4103    |       | ADD A, # 21      | 24,21    | Get the second data        |

| 4105    |       | MOV DPTR, # 4500 | 90,00,45 | Initialize the DPTR        |

| 4108    |       | MOVX @ DPTR, A   | F0       | Store the result in memory |

| 4109    | HLT   | SJMP HLT         | 80, FE   | Stop the program           |

**OUTPUT:** 4500 - 41

#### **B) SUBTRACTION**

| ADDRESS | LABEL | MNEMONICS        | OPCODE   | COMMENTS                   |

|---------|-------|------------------|----------|----------------------------|

| 4200    |       | CLR C            | C3       | Clear carry flay           |

| 4201    |       | MOV A, # 20      | 74,20    | Move data 1 to Acc         |

| 4203    |       | SUBB A, # 10     | 94,10    | Subtract data 2from data 1 |

| 4205    |       | MOV DPTR, # 4600 | 90,46,00 | Initialize DPTR 4600       |

| 4208    |       | MOV X @ DPTR, A  | F0       | Store the result           |

| 4209    | HLT   | SJMP HLT         | 80,FE    | STOP the program           |

**OUTPUT**: 4600-10

# C) MULTIPLICATION

| ADDRESS | LABEL | MNEMONICS        | OPCODE                       | COMMENTS                                  |  |

|---------|-------|------------------|------------------------------|-------------------------------------------|--|

| 4300    |       | MOV A, # 11      | 74,11                        | Move 1 <sup>st</sup> data in 'A' register |  |

| 4302    |       | MOV B, # 88      | 75,88                        | Move 2 <sup>nd</sup> data to 'B' register |  |

| 4305    |       | MUL AB           | A4                           | Multiply two data                         |  |

| 4306    |       | MOV DPTR, # 4700 | 90,00,47                     | Initialize the DPTR                       |  |

| 4309    |       | MOVX @ DPTR,A    | F6                           | Store the LSB                             |  |

| 430A    |       | INC DPTR         | A3                           | Increment DPTR                            |  |

| 430B    |       | MOV A,B          | E5                           | Move 'B' data into 'A'                    |  |

| 430D    |       | MOVX @ DPTR, A   | A F0 Store the MSB of result |                                           |  |

| 430E    | HLT   | STMP HLT         | 80, FE                       | STOP the program                          |  |

**OUTPUT**: 4700: C8 & 4701: 03

#### **DIVISION**

| ADDRESS | LABEL | MNEMONICS        | OPCODE   | COMMENTS                           |

|---------|-------|------------------|----------|------------------------------------|

| 4400    |       | MOV A, # 05      | 74,55    | Move data 1 in 'A' register        |

| 4402    |       | MOV B, # 03      | 75,16    | Move data 2 in 'B' register        |

| 4405    |       | DIV AB           | 84       | Dived in First data in Second Data |

| 4406    |       | MOV DPTR, # 4800 | 90,00,48 | Initialize DPTR                    |

| 4409    |       | MOVX @ DPTR, A   | F0       | Store the LSB                      |

| 440A    |       | INC DPTR         | A3       | Increment DPTR                     |

| 440B    |       | MOV A,B          | E5       | Store count value                  |

| 440C    |       | MOVX @ DPTR, A   | F0       | Store the remained value in DPTR   |

| 440D    | HLT   | SJMP HLT         | 80,FE    | STOP the program                   |

**OUTPUT:** 4800: 01 & 4801: 02

#### **RESULT**

Thus the 8 bit addition, subtraction multiplication and division are executed and output was verified by using microcontroller (8051).

| EXP NO: | INTERFACING OF STEPPER MOTOR |

|---------|------------------------------|

| DATE    | INTERPACING OF STELLER MOTOR |

To interface the stepper motor with microcontroller (8051) and rotate in different speed in clock wise and anticlockwise direction

#### **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | 8051 Trainer Kit                 | 1No      |

| 2    | Power Chord                      | 1No      |

| 3    | Stepper motor interface board    | 1 No     |

#### THEORY:

A motor in which the rotor is able to assume only discrete stationary angular position is a stepper motor. The rotor motion occurs in a stepwise manner from one equilibrium position to next. The motor under our consideration uses 2 – phase scheme of operation. In this scheme, any two adjacent stator windings are energized. The switching condition for the above said scheme is shown in Table.

#### **NOTE**

- 1. Load the given set of data from 4300 onwards.

- 2. Clockwise (09, 05, 06, 0A) H

- 3. Anticlockwise (0A, 06, 05, 04) H

- 4. Load time delay in DE pair.

#### ANTI CLOCK WISE

| step | A1 | <b>A2</b> | <b>B1</b> | <b>B2</b> |    |

|------|----|-----------|-----------|-----------|----|

| 1    | 1  | 0         | 1         | 0         | 0A |

| 2    | 0  | 1         | 1         | 0         | 06 |

| 3    | 0  | 1         | 0         | 1         | 05 |

| 4    | 1  | 0         | 0         | 1         | 09 |

#### **CLOCKWISE**

| step | A1 | <b>A2</b> | <b>B1</b> | <b>B2</b> |            |

|------|----|-----------|-----------|-----------|------------|

| 1    | 1  | 0         | 0         | 1         | 09         |

| 2    | 0  | 1         | 0         | 1         | 05         |

| 3    | 0  | 1         | 1         | 0         | 06         |

| 4    | 1  | 0         | 1         | 0         | 0 <b>A</b> |

#### **PROGRAM:**

| ADDRESS | LABEL  | MNEMONICS        | OPCODE   | COMMENTS                |

|---------|--------|------------------|----------|-------------------------|

| 4100    | START  | MOV DPTR, # 4500 | 90,45,00 | Load the DPTR           |

| 4103    |        | MOV R0, # 04     | 78,04    | Count value in R0       |

| 4105    | UP     | MOVX A,@ DPTR    | E0       | Move the content        |

| 4106    |        | PUSH DPH         | C0,83    | Of DPTR to Acc          |

| 4108    |        | PUSH DPL         | C0,82    | Push the value of       |

| 410A    |        | MOV DPTR, #FFC0  | 90,FF,C0 | DPL & DPH               |

| 410D    |        | MOV R2,#04       | 7A,04    | Move the content        |

| 410E    |        | MOV R1, # 0F     | 79,0F    | of Accumulator to DPTR  |

| 4110    | DELAY2 | MOV R3 # 0F      | 7B,0F    |                         |

| 4112    | DELAY1 | DJNZ R1, DELAY1  | DB,FE    | Decrement Lump NON zero |

| 4114    |        | DJNZ R2, DELAY2  | D9,FA    | R5 to count             |

| 4116    |        | POP DPL          | DA,F8    |                         |

|         |        | MOVX @DPTR,A     | F0       | Pop the value of DPL    |

| 4118    |        | POP DPL          | D0,82    | Pop the value of DPH    |

|         |        | POP DPH          | D0,83    | Increment the DPTR      |

| 411A    |        | INC DPTR         | A3       | Content                 |

| 411B    |        | DJNZ R0, UP      | D8,E4    | DATA                    |

| 411E    |        | SJMP START       | 80,DD    | DATA                    |

#### **OBSERVATION:**

| CLOCK WISE | ANTI CLOCKWISE |

|------------|----------------|

| 4500-09H   | 4500-0AH       |

| 4501-05H   | 4501-06H       |

| 4502-06Н   | 4502-05H       |

| 4503-0AH   | 4503-09H       |

#### **RESULT**

Thus by using the above assembly language program was successfully verified and the direction of motor was controlled using 8051 trainer kit.

| EXP NO: | INTERFACING OF ADC  |

|---------|---------------------|

| DATE    | INTERPACTING OF ADC |

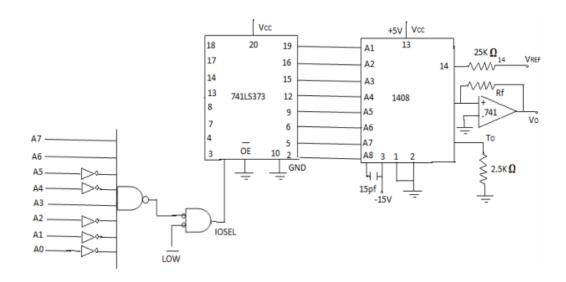

To interface the ADC with 8051 microcontroller and generate the square wave, saw tooth wave and triangular wave.

# **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | 8051 Trainer Kit                 | 1No      |

| 2    | Power Chord                      | 1No      |

| 3    | ADC interface Board              | 1 No     |

#### **CIRCUIT DIAGRAM:**

#### **NOTE**

- 1) Converter the analog signal in to digital and store the result in some memory location.

- 2) 4100 starting of use address.

- 3) 4500 result stored location.

#### **SOC JUMPER SELECTION:**

J2: SOC Jumper selection

J5: Channel selection

# **OBSERVATION:**

Compare the data displayed at the LEDs with that stored at location 4150

# **PROGRAM:**

| ADDRESS | LABEL | MNEMONICS       | OPCODE   | COMMENTS                             |

|---------|-------|-----------------|----------|--------------------------------------|

| 4100    |       | MOV DPTR, #FFC8 | 90,FF,C8 |                                      |

| 4103    |       | MOV A,#10       | 74,10    | Select Channel 0 and<br>make ALE Low |

| 4105    |       | MOVX @DPTR, A   | F0       |                                      |

| 4106    |       | MOV A,#18       | 74,18    | make ALE High                        |

| 4108    |       | MOVX @DPTR, A   | F0       |                                      |

| 4109    |       | MOV DPTR, #FFD0 | 90,FF,D0 |                                      |

| 410C    |       | MOV A,#01       | 74,01    | SOC signal High                      |

| 410E    |       | MOVX @DPTR, A   | F0       |                                      |

| 411F    |       | MOV A,#00       | 74,00    | SOC signal low                       |

| 4111    |       | MOVX @DPTR, A   | F0       |                                      |

| 4112    |       | MOV DPTR, #FFD8 | 90,FF,D8 |                                      |

| 4115    | WAIT  | MOVX A,@DPTR    | E0       |                                      |

| 4116    |       | JNB E0,WAIT     | 30,E0,FC | Check for EOC                        |

| 4119    |       | MOV DPTR,#FFC0  | 90,F,C0  | Read ADC data                        |

| 411C    |       | MOVX A,@DPTR    | E0       |                                      |

| 411D    |       | MOV DPTR,#4150  | 90,41,50 | Store the data in memory location    |

| 4120    |       | MOVX @DPTR, A   | F0       |                                      |

|         | HERE  | SJMP HERE       | 80,FE    |                                      |

#### **OUTPUT:**

| ANALOG<br>VOLTAGE |    | DIGITAL DATA ON LED DISPLAY |    |    |    |    |    | HEX CODE |        |                  |

|-------------------|----|-----------------------------|----|----|----|----|----|----------|--------|------------------|

|                   | D7 | D6                          | D5 | D4 | D3 | D2 | D1 | D0       | OUTPUT | IN LOCATION 4150 |

|                   |    |                             |    |    |    |    |    |          |        |                  |

|                   |    |                             |    |    |    |    |    |          |        |                  |

|                   |    |                             |    |    |    |    |    |          |        |                  |

|                   |    |                             |    |    |    |    |    |          |        |                  |

|                   |    |                             |    |    |    |    |    |          |        |                  |

|                   |    |                             |    |    |    |    |    |          |        |                  |

#### **RESULT:**

Thus the assembly language program to convert an analog signal into a digital has been executed successfully and the digital data was stored at desired location.

| EXP NO: | INTERFACING OF DAC |

|---------|--------------------|

| DATE    | INTERFACING OF DAC |

To interface the DAC with 8051 microcontroller and generate the square wave, saw tooth wave and triangular wave.

# **REQUIREMENTS:**

| S.No | Hardware & Software Requirements | Quantity |

|------|----------------------------------|----------|

| 1    | 8051 Trainer Kit                 | 1No      |

| 2    | Power Chord                      | 1No      |

| 3    | DAC interfacing board            | 1 No     |

| 4    | CRO                              | 1 No     |

#### **CIRCUIT DIAGRAM:**

#### **WAVEFORMS:**

# **SQUARE WAVE**

| ADDRESS | LABEL | MNEMONICS        | OPCODE   | COMMENTS                                 |

|---------|-------|------------------|----------|------------------------------------------|

| 4100    |       | MOV DPTR, # E0C0 | 90,FF,C8 | Move the immediate                       |

| 4103    | START | MOV A, # 00      | 74,00    | Data EOCO Initialize the Accumulator     |

| 4105    |       | MOVX @ DPTR, A   | F0       | To zero                                  |

| 4106    |       | LCALL DELAY      | 12,41,12 | Long call the delay  Move the content of |

| 4109    |       | MOV A, # FF      | 74,FF    | Accumulator to FF                        |

| 410B    |       | MOVX @ DPTR, A   | F0       | Long call delay  Long jump to start      |

| 410C    |       | LCALL DELAY      | 12,41,12 | Move the 05 data                         |

| 410F    |       | LJMP START       | 02,41,03 | To R register  Decrement Jump NON zero   |

| 4112    | DELAY | MOV R1, # 05     | 79,05    | Return to main program                   |

| 4114    | LOOP  | MOV R2, # FF     | 74,FF    | Short jump to start                      |

| 4116    | HERE  | DJNZ R2, HERE    | DA,FE    |                                          |

| 4118    |       | DJNZ R1, LOOP    | D9,FA    |                                          |

| 411A    |       | RET              | 22       |                                          |

| 411C    |       | SZMP START       | 80,E3    |                                          |

# **OBSERVATION:**

| AMPLITUDE | TIME PERIOD |

|-----------|-------------|

|           |             |

#### TRIANGULAR WAVE

| ADDRESS | LABEL | MNEMONICS        | OPCODE   | COMMENTS                                      |

|---------|-------|------------------|----------|-----------------------------------------------|

| 4100    |       | MOV DPTR, # FFC8 | 90,FF,C8 | Initialize the DPTR                           |

| 4103    |       | MOV A, # 00      | 74,00    | Content. Initialize Accumulator value is zero |

| 4105    | LOOP  | MOVX @ DPTR, A   | F0       | Increment accumulator                         |

| 4106    |       | INC A            | 04       | Content  Move the content                     |

| 4107    |       | JNZ LOOP1        | 70,FC    | Of Accumulator FF                             |

| 4109    |       | MOV A, # FF      | 74,FF    | Decrement the Accumulator Content             |

| 410B    | LOOP2 | MOVX @ DPTR, A   | F0       | Long Jump to Start                            |

| 410C    |       | DEC A            | 14       |                                               |

| 410D    |       | JNZ LOOP2        | 70,FC    |                                               |

| 410F    |       | LJMP START       | 02,41,03 |                                               |

#### **OBSERVATION:**

| AMPLITUDE | TIME PERIOD |

|-----------|-------------|

|           |             |

#### **SAWTOOTH**

| ADDRESS | LABEL | MNEMONICS        | OPCODE   | COMMENTS |

|---------|-------|------------------|----------|----------|

| 4100    |       | MOV DPTR, # FFC8 | 90,FF,C8 |          |

| 4103    |       | MOV A, # 00      | 74,00    |          |

| 4105    | LOOP  | MOVX @ DPTR, A   | F0       |          |

| 4106    |       | INC A            | 04       |          |

| 4107    |       | JNZ LOOP         | 80,FC    |          |

#### **OBSERVATION:**

| AMPLITUDE | TIME PERIOD |